Achieving a sub-microsecond latency may be difficult in conventional trading applications. We have been taught to build the systems that are easy to test – separating architectural layers, frameworks and processes. The best software engineering practice would call to design, build and test order management operations, market data processing, risk control and logic of trading algorithms independently from each other. Conventional design makes perfect sense in the most cases. But it may also introduce significant limitations in high-frequency trading (HFT) applications.

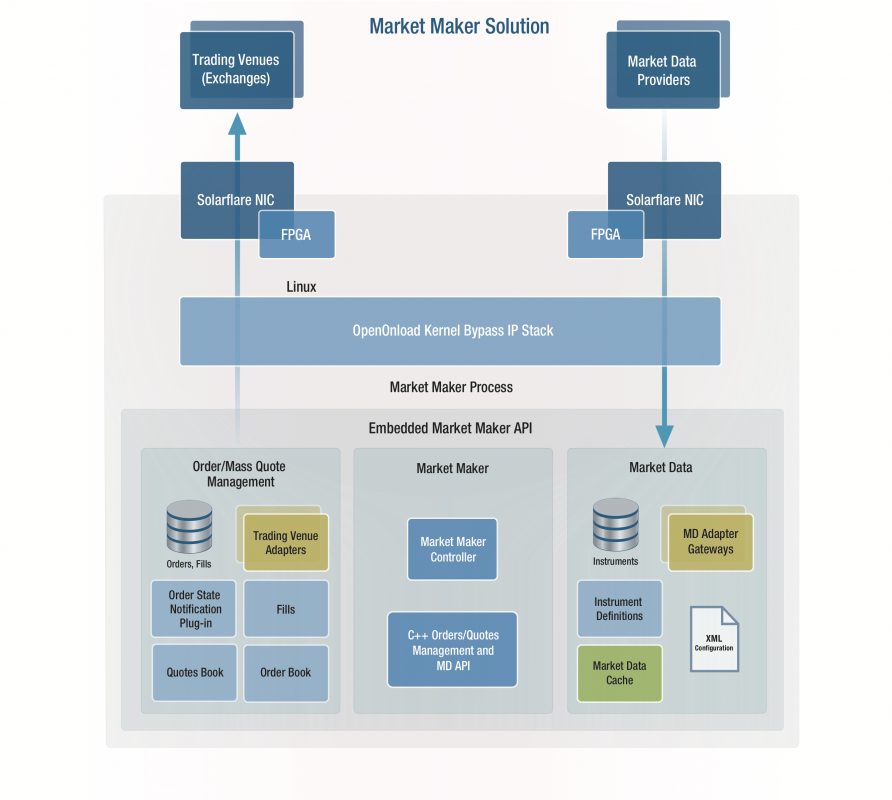

We were facing a significant architectural challenge in one of the recent ATP customization projects – a trading infrastructure for one of CME market maker when IPC between Argo Trading Platform servers (OMS, MDF, RMS) became a major obstacle . Our layered design came to rescue. We have “collocated” trading API, order management and market data modules in one process and applied a number tried-and-true performance optimization techniques:

- • build on Linux, taking advantages of myriads OS-specific optimization tricks

- • use the best of the breed network technology and kernel bypass IP stack from Solarflare

- • eliminate data copying – whenever possible

- • pre-serialize FIX messages directed to trading venue

- • refactor data structures to facilitate optimal use of processor cache

- • apply lock-less and block-less design patterns, eliminating OS signaling latency whenever it’s possible

- • utilized OS scheduler interfaces to complete minimize indeterministic behavior of standard thread scheduling algorithms

Our tick-2-order latency satisfies the needs of the most demanding HFT and Market Making applications. It can be used with various FPGA solutions.